1. review

0) 학습 큰 그림

전체적인 datapath와 control의 개념을 먼저 이해하고

명령어와 데이터가 어떻게 관리되는지 아는 것이 이 장의 목표이다.

처음에는 single cycle 디자인부터 시작해서 multi cycle 디자인으로 확장해 나가는 방식으로 학습하는 큰 그림을 그려야함

1) Processor의 구성요소 Datapath, control 개념 정리

컴퓨터 시스템의 연산 기능을 담당하는 하드웨어인 Processor에 대해서 정리한다.

그 중 Datapath와 Control 관점에서 정리할것이다.

대표적으로 사용하는 데스크탑, 스마트폰 등 뿐만 아니라 가전제품의 인공지능, IOT와 같은 컴퓨터 시스템이 일상생활에서도 적용되고 있습니다.

이런 다양한 장치를 컴퓨터에 범주에 포함시켜 말할 수 있는 이유는 이런 모든 장치들이 컴퓨터 구조를 따르기 때문입니다.

소프트웨어 프로그램을 실행하여 동작하는 모든 장치를 컴퓨터라고 부를 수 있습니다.

현대 사용되는 컴퓨터는 Von Neumann architecture를 따르며 이 아키텍쳐는 컴퓨터가 아래 3가지 큰 구조로 구성되어 있다고 정의합니다.

1. 프로세서

2. 메모리

3. 입출력 장치

프로세서는 datapath와 control로 구성되어 있습니다. 그 중 datapath는 말 그대로 데이터가 흘러가는 경로를 의미합니다.

datapath를 통해 흘러가는 데이터를 dataflow라고 합니다.

dataflow를 제어하는 것이 control의 역할입니다.

2) Performance review

아래 3가지 성능과 관련된 용어에 대해 정리를 하겠습니다.

① instruction count

프로그램에 명령어 수를 의미하고 실제 컴퓨터 성능과 밀접한 관련이 있습니다.

② Clock cycle time

clock 주기란 clock 사이클에서 한 주기가 도는데 걸리는 시간을 의미하며 이는 clock frequency(clock speed)와 역수 관계입니다.

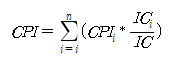

③ Clock cycle per instruction(CPI)

프로그램에서 한 명령어를 수행하는데 걸리는 평균 clock cycles 수를 말합니다.

프로그램을 실행하는데 한 명령어당 clock cycle의 개수가 있을 것입니다.

전체 명령어를 실행하는데는 (각 명령어)*(각 명령어의 clock cycle의 수)로 생각할 수 있으며

이것을 정리해보면

CPU clock cycle의 수 = 명령어의 수 * 명령어 당 clock cycle의 수로 생각할 수 있습니다.

따라서 아래의 CPI를 구하는 공식이 됩니다.

위 식에서 IC는 프로그램의 전체 명령어 수를 의미합니다. IC(i) 는 각 명령어 타입별로 있는 명령어 개수입니다.

2. Single-cycle datapath

1) Processor execution cycle

● Processor execution cycle의 개념

Processor execution cycle이란 위에서 살펴본 MIPS 명령어를 예시로 하면 명령어들이 프로세서에서 어떤 순서와 절차로 실행되는지에 대해 알아보는 것입니다.

Processor execution cycle이 반복적으로 실행되면서 소프트웨어가 실행되게 되는 것입니다.

무수히 많은 프로세스의 명령어들이 control flow에 따라 하나씩 Processor execution cycle에 의해서 실행되는 것입니다.

아래 단계는 각 명령어들이 실행될 때 어떻게 실행되는지 절차를 정리한 것입니다.

아래의 전체 과정을 1개의 Clock Cycle에서 수행한다고 해서 Single cycle datapath라고 합니다.

① step1 : Instruction fetch

제일 먼저 실행할 명령어를 instruction 메로리로부터 읽어들어오는 작업을 합니다. 이것을

Instruction fetched 단계라고 합니다.

소프트웨어 프로그램 명령어를 가리키고 있는 즉 PC 값이 가리키고 명령어의 메모리 주소를 하나 읽어들이는 과정이 됩니다.

② step2 : Instruction decode

명령어를 CPU로 fetch (읽기)를 했다면 이 명렁어를 Instruction decode 과정을 거치게 되는데 이 과정에서 op코드가 무엇인지 피연산자가 무엇인지 어떤 레지스터를 사용하는지 immediate 값이 무엇인지를 분석하게 됩니다.

op코드에서 datapath를 제어할 control unit의 컨트롤 정보를 만들게 됩니다.

또한 branch 명령어같은 경우는 PC 값의 업데이트가 진행되기도 한다.

③ step3 : operand fetch

R-format의 add 명령어를 보면 rd, rs, rt 3개의 레지스터를 사용하는데 먼저 두 피연산자를 저장한 rs와 rt 레지스터를 연산을 위해 읽어오는 작업을 합니다. 이 과정이 operand fetch라고 합니다.

피연산자를 가진 레지스털르 fetch(읽어)들여서 ALU로 전달한다.

④ step4 : Execute

add, sub와 같은 ALU 연산이 레지스터에 fetch된 값을 통해 ALU가 수행하게 됩니다.

⑤ step5 : Result Store

이렇게 연산이 수행된 후 연산의 결과가 레지스터 rd 또는 메모리에 저장됩니다.

PC값이 다음 명령어를 가리키도록 합니다.

위와 같은 5가지 step이 반복적으로 진행되면서 프로그램이 실행되게 되는 것입니다.

● Processor execution cycle 다이어그램

위에서 정리한 Processor execution cycle의 순서를 다이어그램으로 정리한 것입니다

3. Register file

1) Register file

Processor design에서 레지스터 파일을 사용하는데 레지스터 파일은 MIPS를 기준으로 32개의 32bit로 이루어져있습니다.

● Two 32bit output busses

operand fetch 단계에서 산술 연산을 위해서 ALU로 두 레지스터의 값을 ALU로 보내야하기 떄문에 레지스터 파일은 2개의 32bit output busses를 가집니다.

Read data1, Read data2로 부를 수 있다.

● One 32bit input bus

또한 ALU의 연산된 결과를 레지스터 파일에 다시 쓰기 위해서 레지스터 파일은 하나의 input bus를 가집니다.

Write Data로 부를 수 있다.

● Read register1, Read register2, Write register

레지스터 파일은 입력 포트 3개를 가지는데 각각의 데이터를 출력하고 입력 받는 레지스터를 선택하기 위해서 레지스터의 주소를 지정하기 위한 Read register1, Read register2, Write register 3개의 입력 포트를 가지고 있습니다.

2) Register File의 동작 원리

● 레지스터 파일 -> ALU (Read operation)

레지스터에 산술연산을 위한 피연산자가 저장되어 있는 상태에서 이 레지스터의 값을 ALU로보낼 때는 두 피연산자는 레지스터 파일의 2개의 output busses로 나가게 되는데

output busses로 나갈 두 레지스터를 지정하는 포트인 Read register1, Read register2가 가리키는 레지스터를 ALU연산을 위해 내보냅니다.

● ALU -> 레지스터 파일 (Write operation)

이제 ALU 산술이 끝나서 ALU의 결과를 레지스터 파일에 다시 쓰는 경우에는 레지스터 파일의 RegWrite라는 control 신호의 값이 1로 셋팅되고 이 값이 1이라면 어떤 레지스터에 쓸지는 Write register 가 가리키는 레지스터의 주소에 ALU 결과를 쓰는데 Write Data라는 하나의 input 포트를 통해 데이터가 레지스터 파일에 들어와 써지게 됩니다.

● Clock input (CLK)

Processor design에서 레지스터 파일은 Write operation이 clock에 동기화 되어서 동작하게 됩니다.

Read operation 같은 경우는 Read register1, Read register2로 주소가 지정되면 바로 Read operation이 동작해 Clock 신호에 영향을 받지 않습니다.

4. Storage element : Memory

1) Memory File

메인 메모리는 (캐시 메모리를 제외한) 프로세서 외부에 존재하게 됩니다. 따라서 메인 메모리 RAM에 접근하는데는 CPU 속도와 상대적으로 많은 시간이 소요됩니다.

메모리를 개념적으로 File화 해서 정리하겠습니다

● Address 포트

read write할 메모리의 주소를 가리키는 포트가 있습니다.

● Read data

메모리에서 Address 포트가 가리키는 주소의 값을 읽어서 외부로 내보내는 포트인 Read data 포트가 있습니다.

● Write data

이 포트는 store 과정에서 메모리로 쓰기 위한 데이터가 들어오는 포트입니다.

● MemRead

메모리를 추상적인 개념인 파일로 표현할 때 MemRead라는 control 신호가 1로 지정이 되면 Address가 지정하는 메모리 주소의 메모리 공간을 Read data 포트로 출력합ㄴ디ㅏ.

● MemWrite

MemWrite라는 control 신호가 1로 지정이 된다면 Write data 포트로 공급되는 데이터가 메모리에 저장되게 됩니다.

● clock input (CLK)

Write 동작은 역시 Clock 신호에 동기화되고 Read 동작은 Clock 신호에 무관합니다.

하지만 메모리 파일은 접근 시간이 느리기 때문에 Read 동작은 약간의 access time이 지연됩니다.

5. Processor execution cycle의 동작을 Processor design 관점에서 정리

Processor execution cycle의 각 단계별로 processor design이 각 컴포넌트 별로 어떻게 동작하는지에 대해 설명 드리겠습니다.

1) Instruction fetch 단계

Processor execution cycle의 첫 번 째 단계인 Instruction fetch 단계에서 Processor design 관점에서 정리하면,

Instruction fetch단계는 PC와 명령어가 저장되어 있는 메인 메모리를 중심으로 동작합니다.

명령어를 fetch하는 과정은 ‘메모리 파일’의 Addrss 포트에 할당된 즉 Address 포트값이 가리키는 주소의 메모리 값을 읽어서 메모리 파일에서 데이터를 외부로 내보내는 포트인 Read data 포트를 통해 명령어를 내보내 instruction을 PC 에 fetch할 수 있게 됩니다.

Processor execution cycle이 끝났으면 다음 Processor execution cycle단계에서 fetch할 PC의 값을 결정해줘야하는데

PC = PC + 4로 결정딥니다. 4는 4byte를 의미하며 branch 와 같은 명령어가 아니라면 명령어가 저장된 메모리에서 순차적으로 메모리의 명령어가 실행됩니다.

2) Execute 단계

add, sub와 같은 ALU 연산이 레지스터에 fetch된 값을 통해 실제로 ALU를 통해 연산이 실행되는 과정입니다.

레지스터 파일에서 Read data1, Read data2 출력 포트를 통해 레지스터 파일에 Read register1, Read register2가 가리키는 레지스터의 값을 ALU로 출력하게 됩니다.

그럼 ALU에서 연산이 이루어지게 됩니다. 그리고 연산이 다 되면

레지스터 파일의 RegWrite 이라는 control 신호가 1로 셋팅되고 ALU의 결과를 레지스터 파일의 Write data 포트를 통해 들어와 레지스터에 저장됩니다.

3) R-format RTL : add

add 명령을 통해 R-foramt RTL을 설명합니다.

각각의 명령어에 RTL에 대해서 Instruction fetch나 Execute 과정에서 unit들이 어떻게 동작하는지 정리하겠습니다. add rd, rs, rt 의 형태가 add 명령형태입니다.

※ 헷갈릴거 정리

- add rd rs rt => rd = rs + rt

R-format에서는 rd레지스터가 저장되는 레지스터고 두 피 연산자는 rs, rt이다. - ori rt, rs ,1200

I-format에서는 rt가 저장되는 레지스터고 두 피연산자는 rs, 1200(imm)이다.

① Instruction fetch

프로세스 명령어들이 저장된 메모리에서 PC로 명령어의 주소를 fetch하게 됩니다.

② Instruction decode / operand fetch

decode 단계에서 위 MIPS 명렁어가 add 명령어란 것을 판단하고

뒤에 따라오는 피연산자의 값을 레지스터 rs, rt로 fetch합니다.

③ Execute / Result Store

add, sub와 같은 ALU 연산이 레지스터에 fetch된 값을 통해 ALU가 수행하게 되고 Rsult Store 단계에서 ALU의 연산 결과가 저장됩니다.

그리고 PC <- PC + 4를 하여 다음 명령어로 PC를 업데이트 합니다.

4) I-format RTL : ori

ori $rt, $rs, 1200 이라는 명령어는 우선

1200을 2진수로 변환해서 $rs과 or 연산을 한 뒤 $rt에 저장합니다.

① Instruction fetch

프로세스 명령어들이 저장된 메모리에서 PC로 명령어의 주소를 fetch하게 됩니다.

② Instruction decode / operand fetch

decode 단계에서 위 MIPS 명렁어가 ori 명령어란 것을 판단합니다.

I-format에서는 R-format과 다르게 operand fetch하여 레지스터의 값을 저장하는 방법이 다른데,

imm의 연산을 지원하기 위해 R-format에서는 필요없던 2개의 추가적인 mux(mux1, mux2)가 더 필요하게 됩니다.

그 이유는 R-format은 [op rs rt rd] 형태로 rs, rt, rd가 각각 Read register1, Read register2, write register 포트로 연결되는데,

I-format은 [op rs rt imm] 형태로 Write data 포트가 rt 레지스터로 연결되야하기 때문입니다.

따라서 이 두 가징 경우를 컨트롤 할 RegDst 컨트롤 신호와함께 Mux1가 필요한 것입니다.

RegDst가 1이면 R-format이고 0이면 I-foramt으로 컨트롤합니다.

그리고 나머지 하나의 추가 Mux2는 16bit immediate 값이 Mux2와 ALUSrc 컨트롤에 제어로 ALU로 인가되게 됩니다.

ALUSrc값이 0이면 R-format으로 컨트롤하고 1이면 I-format으로 컨트롤하는데 16bit imm의 값을 32bit로 변경해주는 sign extend를 거쳐 변환되어 ALU로 들어가게 됩니다.

※ 자세히 설명

R-foramt에서는 [op rd rs rt] 이렇게 op 코드와 함께 3개의 레지스터가 rd는 결과 값을 저장하는 레지스터로 Write data 포트로 연결되었고 rs, rt는 피연산자로 Read register1, Read Register2 포트로 연결되었습니다.

하지만 I-format의 명령는 [op rs rt imm]의 형태로 rs에는 base가 들어있고 rt에 결과 값을 저장하는 구조입니다. 따라서 RegDst가 0으로 지정되면 Mux1의 작용으로 레지스터의 Write register로 rt 레지스터가 연결되고 값이 저장되게 됩니다.

rs의 값은 기존의 Read register 포트로 rs 레지스터를 연결하여 base 값을 R[rs]에 저장합니다.

그리고 Mux2와 ALUSrc는 immediate에서 올라오는 신호를 택할지 R-format에서 피연산자를 저장한 레지스터를 택할지를 결정하는 컨트롤 신호와 mux2가 됩니다.

③ Execute / Result Store

add, sub와 같은 ALU 연산이 레지스터에 fetch된 값을 통해 ALU가 수행하게 되고 Rsult Store 단계에서 ALU의 연산 결과가 저장됩니다.

그리고 PC <- PC + 4를 하여 다음 명령어로 PC를 업데이트 합니다.

5) I-format RTL : lw

● Load RTL

Load 명령어는 I-format을 사용합니다.

lw rt rs(imm) 이와 같은 laod 명령이 있다고 가정하겠습니다.

이 것은 rs 레지스터에는 base의 주소값이 들어있고 imm는 offset을 의미하며 load하여 저장시킬 레지스터를 rt로 지정한 것입니다.

① Instruction fetch

PC에 저장된 값으로부터 CPU로 명령어를 fetch를 우선합니다. 레지스터 파일의 Write data 포트를 통해 레지스터 파일로 base 값이 들어오며 저장됩니다.

② Instruction decode / operand fetch

decode 단계에서 위 MIPS 명렁어가 load 명령어란 것을 판단하고

베이스 레지스터에 값을 R[rs] 레지스터로 fetch 합니다.

③ Execute / Result Store

ALU 연산이 레지스터에 fetch된 R[rs] 레지스터가 공급되고

레지스터 파일의 ALUSrc 값이 1로 셋팅되어 offset 값인 imm값 16bit에서 32bit으로 Sign-extend에 의해 변경되고 역시 ALU로 전달 됩니다. 그 후

ALU 내부에서 R[rs] + SignExt(imm16) 작업을 수행하고 메모리 파일로 접근을 합니다.

이때 메모리 파일의 Address 포트에 R[rs] + SignExt(imm16)이 값을 저장하고 메모리 Read data 포트로부터 Address 포트가 가리키는 값을 ALU로 받게 됩니다. 그럼 ALU에서는 메모리로부터 받은 값을 레지스터 R[rt]에 저장하게 되어 메모리에 있는 값을 레지스터로 load할 수 있게 됩니다.

5) I-format RTL : beq

● Branch RTL

branch 명령어 중 아래 명령어를 예시로 설명 드리겠습니다.

beq rt, rs, imm 16

우선 위 명령어는 rt의 값과 rs의 값이 같다면 PC + 4 +64 로 PC를 변경하라는 의미가 됩니다.

① Instruction fetch

PC에 저장된 값으로부터 CPU로 명령어를 fetch를 우선합니다.

② Instruction decode / operand fetch

decode 단계에서 위 MIPS 명렁어가 beq 명령어란 것을 판단하고

뒤에 따라오는 두 피연산자의 값을 레지스터 rs, rt로 fetch한다.

③ Execute / Result Store

beq 연산은 두 값을 빼서 결과가 0이라면 같음을 의미하도록 하는 방식으로 ALU 연산을 합니다. 이때 ALU에저 zero states flags를 사용하여 두 레지스터의 뺄샘 연산이 0일 경우 zoro flags는 1로 셋팅됩니다. 만약 뺄셈의 연산이 0이 아니라면 zero flags는 0으로 셋팅 되어 beq 수행을 ALU가 수행할 수 있게 됩니다.

만약 zero flags 값이 1이라면 명령어로 주어진 imm 값 만큼 PC에 더해줘야하는데

PC <- PC + 4 + (SignExt(imm15) <<2); 이와 같은 방식으로 PC의 값을 변경시킵니다.

16bit imm값은 zero 가 1이 되면 Sign-extend에 의해 32bit로 변형되고 shift left 2를 거쳐 PC + 4에 (SignExt(imm15) <<2) 이 값이 더해지게 됩니다.

만약 zero flags 값이 0이면 PC <- PC + 4; 를 합니다.

5. Single cycle Control Signal정리

| Signal | Dscription |

| RegDst | 레지스터 파일에 앞부분에 존재하는 신호로 destination register를 결정하기 위한 신호이다. |

| RegWrite | 레지스터 파일에 데이터를 쓸지를 control 한다. |

| ALUSrc | 이 값을 통해 immediate 또는 소스 레지스터 둘 중 하나를 ALU로 값을 공급함. 만약 ALUSrc가 1이면 immedata를 ALU로 공급하고 0이면 소스 레지스터를 공급함. |

| ALUOp | ALU에서 수행할 연산을 결정한다. |

| MemWrite | 메모리 파일에 데이터를 쓰기 위해 MemWrite 값이 1로 셋팅 됩니다. |

| MemRead | 메모리 파일에 데이터를 읽어 출력하기 위해 MemRead 값이 1로 셋팅 됩니다. |

| MemtoReg | load 명령을 통해 메모리부터 읽은 데이터를 레지스터에 쓸지, ALU의 연산 결과를 레지스터에 쓸지를 결정하는 control 신호임 |

| PCSrc | 이 값은 branch를 통해 PC 값을 변경할지 PC + 4(next PC)를 할지 결정하는 신호이다. |

'전공 > 컴퓨터 구조' 카테고리의 다른 글

| 7. Pipeline에서 데이터 처리 (0) | 2021.12.27 |

|---|---|

| 5. CPI 계산과 CPU time 구하기 (0) | 2021.12.27 |

| 4. Calling Convention(Caller-save, Callee-save, Hybrid) (0) | 2021.10.07 |

| 3. MIPS 문법 정리 (0) | 2021.10.07 |

| 2. ISA란? (0) | 2021.10.07 |